应用设计电源系统时,设计人员必须考虑此类应用固有的宽频率范围,从稳压器中的中频到

内核中的高时钟频率。这种端到端的全双工设计对于优化电源、电源转换和配电过程的性能至关重要。

本文重点介绍如何实现高效的(PDN) 设计。PDN 由连接到电压轨和接地轨的所有组件组成,包括电源和接地层布局、无源元件、IC

以及连接或耦合到主电源轨的任何其他铜质元件。在设计过程中,必须考虑 PDN 中组件的寄生行为,因为这会影响整个系统行为。

旁路和去耦电容是 PDN 中必不可少的元件。因此,PDN 设计中的电容器选择和放置需要特别考虑,因为电容不足会导致系统不稳定和性能问题。

旁路电容器用于稳压器模块(VRM),通过滤除输入纹波电流转换器提供低阻抗电压源。它们还可以补偿电源耦合到 IC

在降压稳压器的输出端,去耦电容的主要目的是保证输出电压(V外) 通过降低输出电压纹波 (∆V

保持恒定外).因此,选择电容以限制∆V外到负载输入规格设定的幅度,同时还考虑与转换器负载突然变化引起的电压变化相关的限制。

旁路电容器是确保降压转换器可靠运行的最重要元件。放置IC后,旁路电容器是布局中放置的第一个元件,必须在IC放置后立即布线。由于不正确的布线而导致的额外寄生电感与转换器的开关相结合,会产生过大的电压尖峰,这可能导致IC故障。

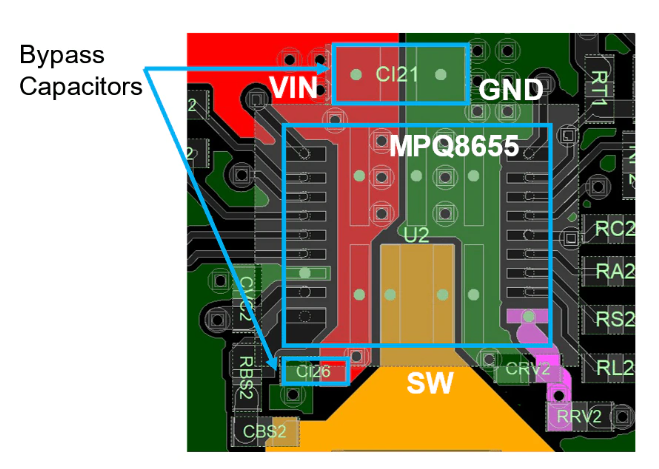

图1显示了负载点(PoL)转换器旁路电容(CI21和CI26)的最佳放置。

旁路电容器环路中产生的寄生电感可分为两部分:电容器的寄生电感和电感和IC之间的电流路径布局产生的电感。由于PCB布局几何形状产生的电感相对于总电感比固有电容器电感更重要,因此设计工作应重点关注。

为了最小化环路电感,旁路电容应尽可能靠近IC放置。还应使用过孔将电容器的焊盘直接连接到电源 (PWR) 和接地 (GND) 网络,尽可能靠近 IC 引脚,从而最大限度地减少电流路径。

所需的去耦电容类型和数量取决于电容在频域中的行为。去耦电容设计用于最大限度地降低VRM的∆V外这是由转换器的开关操作产生的,以及以高频向FPGA/ASIC提供瞬时电流,直到电源可以响应。因此,必须考虑整个工作频谱。

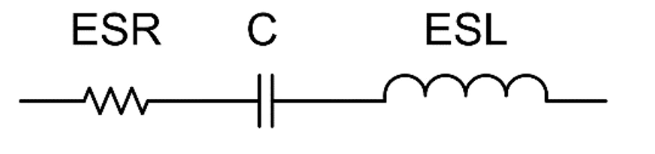

基本电容模型包括三个关键要素:电容 (C)、等效串联电阻(ESR) 和等效串联电感 (ESL),如图2所示。

ESR由元件中导电元件的阻抗引起,并决定了谐振频率处的最小阻抗。ESL由流过电容器的电流的影响产生,并决定谐振频率。谐振频率是电容器阻抗曲线中元件开始表现得像电感器的点,阻抗与频率成比例地增加。

在低频(高达50 kHz)下,降压转换器具有低阻抗。然而,降压转换器在高频下的阻抗主要是感性的。添加到PCB中的每个电容器都会降低给定频率下的PDN阻抗,这意味着精确的放置和选择可以实现设定的目标阻抗曲线。因此,通过从检测点进行测量,可以在给定频率下满足目标阻抗。

其中 ∆V噪声是最大允许纹波电压和ITRANSIENT_MAX是转换器必须提供的最大负载步长。还可以计算所需的输入和输出电容。

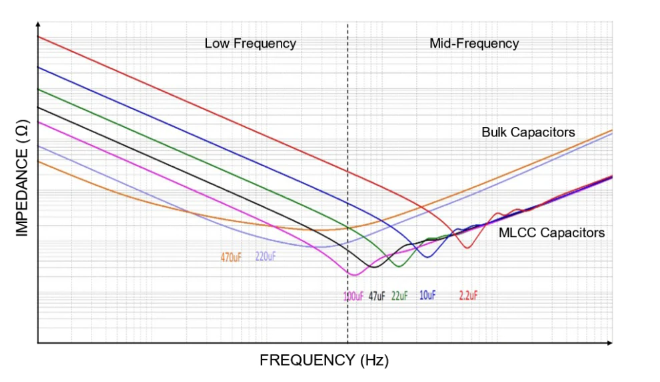

为了将阻抗保持在目标水平以下,必须约束设计并降低寄生电感。大容量电容器在高达 10 MHz 的频率范围内降低阻抗,而MLCC电容器在中高频范围内降低阻抗。

图3图中显示了典型大容量电容器和MLCC电容器的阻抗频率特性。来源:单片电源系统

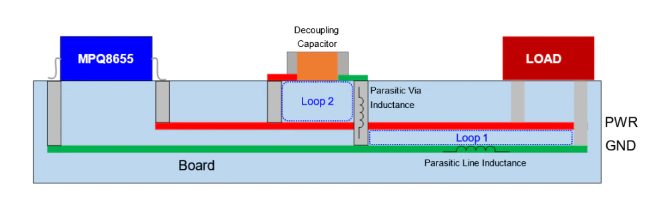

一旦计算和分析了电容,去耦电容在PCB中的最佳位置就很重要。布局几何形状、通孔布局和距离主要影响电源层环路电感,从而影响PDN响应。图4显示了转换器、去耦电容和负载产生的电流环路。由于这些回路是结构固有的并且不可避免,因此尽可能减少这些回路至关重要。

环路1是水平环路分量,由转换器和去耦电容之间的距离决定。环路 2 是垂直环路组件,由将电容器连接到电源层的通孔高度决定。电源层通常放置在PCB的最内层。

该测试板在双相操作中使用两个PoL转换器,V外0.9 V 和最大输出电流 (IOUT_MAX) 的 50 A,这是 ASIC/FPGA 电源轨的通用值。可以使用测试板进行不同场景的仿真,以确定电容器的最佳放置。

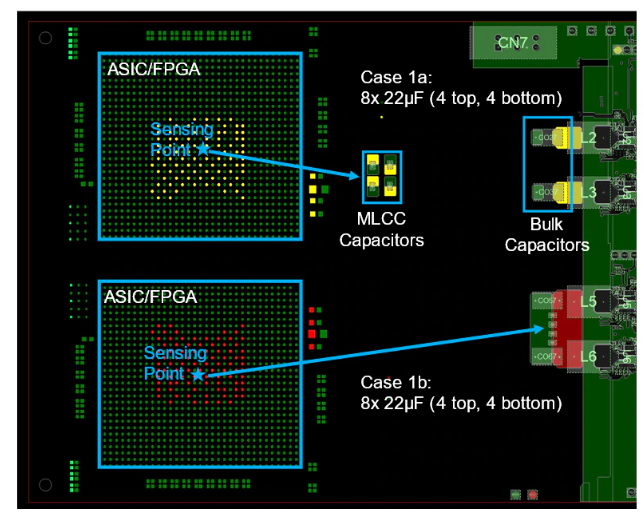

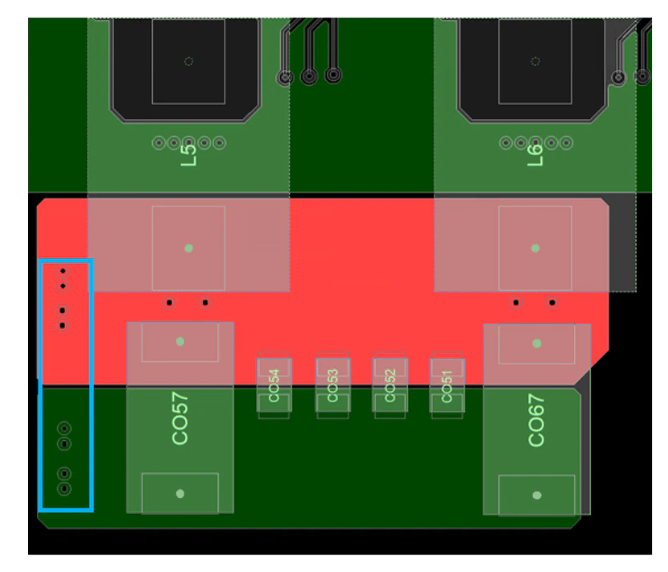

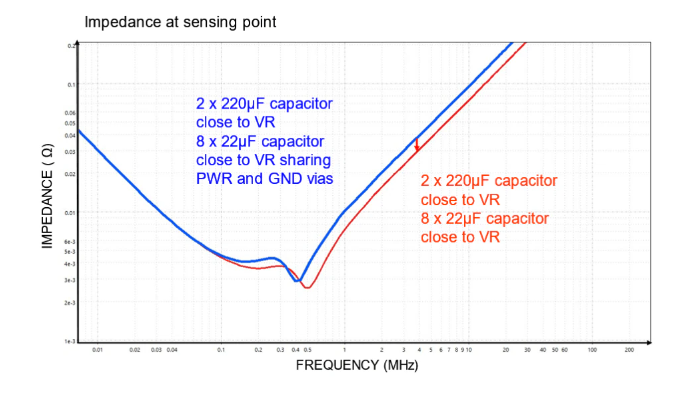

为了评估最佳电容布局,在ASIC/FPGA中心的板级检测点测量阻抗。使用公式1的分析,可以使用8 x 22 μF MLCC电容和2 x 220 μF大容量电容实现VRM阻抗曲线。为了保持稳压器的稳定性,大容量电容器紧跟在输出电感器之后。测试板考虑了22 μF MLCC电容在外壳1a和案例1b下的不同位置(见图5)。

在情况1a中,MLCC电容器放置在ASIC/FPGA之前,从而减小了环路1的尺寸。在案例1b中,MLCC电容器放置在大容量电容器旁边,因此MLCC电容器与传感点之间的距离是案例1a的两倍。

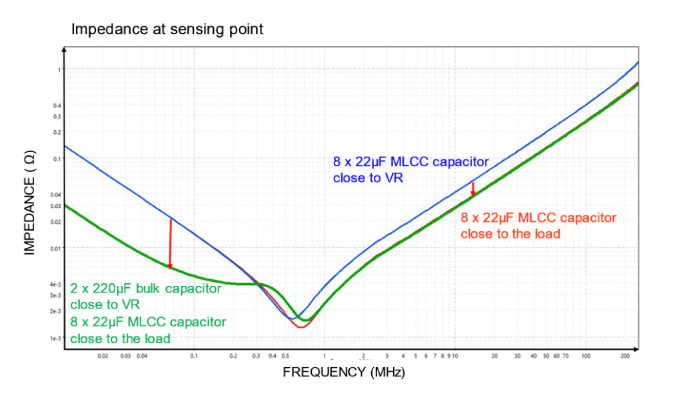

图6显示了将大容量电容放置在降压转换器附近时的仿真结果,这导致低频范围内的阻抗降低(绿色迹线)。将MLCC电容器放置在靠近负载的位置(红色迹线)可降低高频范围内的阻抗,从而使电容器能够更有效地提供FPGA/ASIC负载所需的瞬时电流阶跃。

传统设计指南建议将去耦电容放置在PCB的底部,以减小电路板空间,从而提高功率密度。然而,将电容器放置在电路板底部需要更长的过孔才能到达ASIC/FPGA所在的另一侧。这增加了垂直路径的大小,如图 4 所示,如环路 2 所示。

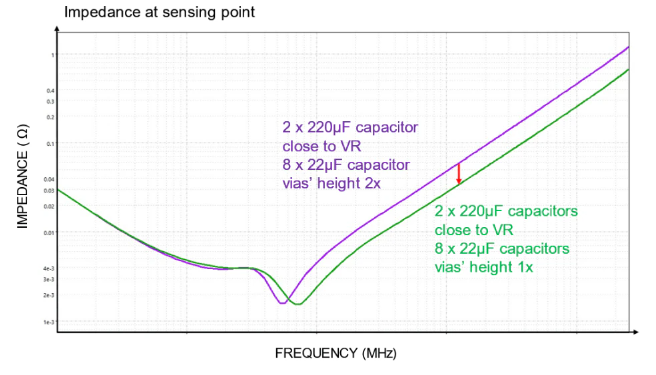

通过将过孔高度加倍进行了额外的测试,以分析增加环路 2 尺寸的效果。图7显示了环路2尺寸变化的测试结果,其中观察到类似的趋势,通孔高度增加导致中高频范围内的阻抗增加。

最小化去耦电容中的环路电感与电容数量同样重要。有两种方法可以实现降低环路电感。第一种方法是减小IC和电容器之间的水平距离。第二种方法是通过将电源层和接地层放置在上层来降低通孔高度。

在小范围内放置多个元件以减少电路板空间通常会导致电容共享过孔。当电容器共享过孔时,如果不考虑通孔定位和数量,正确选择和定位的整体改进可能会显着降低甚至可以忽略不计。因此,通孔布局设计也是降低环路阻抗的关键。

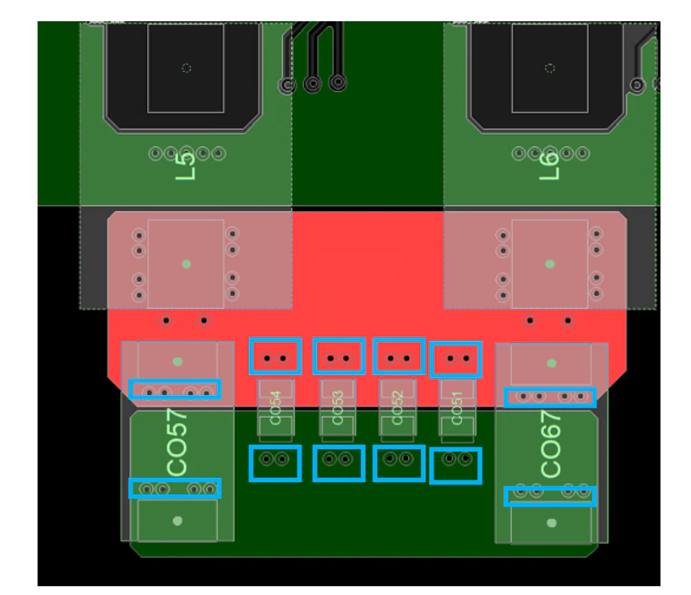

为了分析过孔定位和数量的影响,使用电路板进行了第二次测试,通过放置两个通用设计建议。在第一个设置中,每个电容都有自己的一组通孔连接到电源和接地层(见图8)。

图10显示了通孔放置变化的测试结果。将过孔放置在远离电容的位置会增加环路1的尺寸,从而增加环路电感。因此,过孔共享增加了高频阻抗。

根据后续测试,建议在0805和0603封装中,大容量电容器至少使用4个电源通孔和4个接地过孔,MLCC电容器至少使用2个电源过孔和2个接地过孔。过孔应尽可能靠近电容器放置。

在设计 FPGA/ASIC 系统或任何需要高电流和快速负载瞬变的电路时,必须全面考虑 PDN,以优化系统性能。快速负载阶跃,例如在FPGA中观察到的阶跃,会在整个电路中产生强大的高频电流。在如此高的频率下,PDN 中通常可以忽略的寄生元件可能会突然导致设备故障。设计人员必须注意确保 PDN 的寄生元件最小化。

本文重点介绍如何使用PoL转换器降低VRM去耦电容中的电流路径引起的寄生阻抗。为了获得最佳性能,垂直轴和水平轴上的电流环路应尽可能短。将电流环路放置在尽可能靠近负载的位置,并将电源走线保持在外层,可有效减少通孔长度。

适当的过孔放置也是降低寄生电感的关键。因此,建议在尽可能靠近每个电容器焊盘的位置放置多个过孔,以减少过孔的总寄生电感以及流过每个过孔的电流。

,系统设计人员不断尝试降低总功耗。一般而言,ADC 制造商建议采用低噪声 LDO(低压差)稳压器为 GSPS(或 RF 采样)ADC

,特别是传输和分配(T&D)子站。为能够支持自动化,设备应具有监视和控制功能,确保能够实时

承受着提供足够性能的巨大压力。对于功耗和热管理而言,主要有两种方法可以改善

) 的复杂性可能会因负载的数量和类型、整体系统架构、负载功率级、电压等级(转换级)以及隔离和稳压要求的不同而不同。许多电源系统设计人员将

1.首先参考芯片的参考设计,设计原理图,一般copy就可以;针对特殊情况,可以优化设计,优化去耦电容;2.设计叠成结构,GND与电源层越近越好,建议参考demo;3.放置去耦电容;4.连接去耦电容;5.布线关键电源

AD9175出色的动态性能。噪声目标是基于图3和图4所示的最大允许波纹阈值。优化的配

) 的负担日益增大。使用直流压降分析可确保最佳性能并避免产品故障和失效。

。 电路板上的所有有源电子组件都需要电源才能运行,为此,PCB需要设计良好的电源传输

的必要性 电路板上的所有有源电子组件都需要电源才能运行,为此, PCB 需要设计良好的电源传输

VL53L4CD TOF开发(4)----单次测量(One-Shot)模式

Smaller and smarter motor control drives HEV_EV market forward

【Vision Board创客营连载体验】基于RA8D1-Vision Board的自动路径规划小车